-

CN

-

Service Hotline

+8618129931046 Mr. Liao

Time:2025-07-03 Views:1

Server motherboards are among the most complex PCB designs, requiring multilayer structures (often 16–30 layers) to support high-density component placement, high-speed signal routing, and robust power distribution. Multilayer boards (MLBs) enable strict separation of signal, power, and ground planes, ensuring reliability in 24/7 data center environments.

Key design considerations:

Layer Stackup:

Signal Layers: High-speed traces for CPU-to-memory interfaces (e.g., DDR4/DDR5), PCIe 5.0, and NVMe SSDs require controlled impedance (e.g., 50Ω single-ended, 100Ω differential). Stripline or microstrip routing is used, with embedded capacitors in some layers for power integrity.

Power Planes: Dedicated layers for VCC, VDD, and ground (e.g., 4–6 power layers) distribute power to CPUs, GPUs, and ASICs. Plane capacitance and decoupling capacitors (placed every 10–20 mm) reduce voltage ripple.

Thermal Layers: Copper planes or thermal vias conduct heat from power-hungry components (e.g., voltage regulators) to heat sinks, preventing hotspots.

High-Speed Signaling:

PCIe 5.0 operates at 32 GT/s, requiring low-loss materials (e.g., Isola FR408HR, Rogers 4360) with low dielectric constant (Dk) and dissipation factor (Df). Backdrill technology removes stub remnants from vias to reduce signal reflections.

Memory channels (e.g., DDR5) use fly-by topology with controlled stub lengths and termination resistors to minimize skew and crosstalk.

Component Placement:

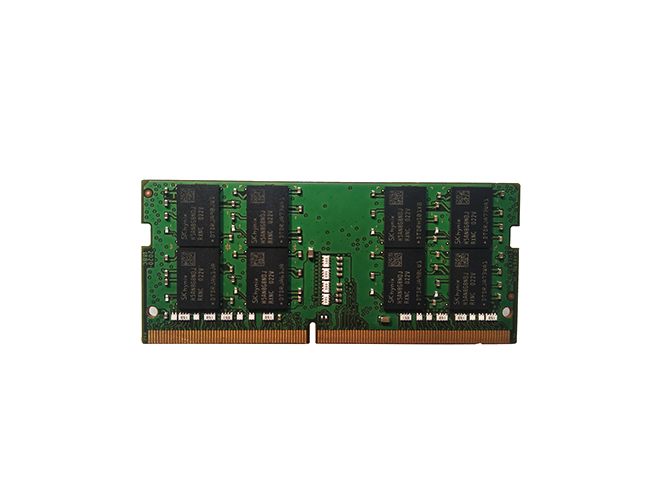

CPUs (e.g., Intel Xeon, AMD EPYC) and GPUs are placed at the center, surrounded by DDR5 DIMM slots and NVMe storage interfaces. High-power components (e.g., voltage regulators) are positioned near the edge for easy heat sink attachment.

Redundant power paths and hot-swap connectors (e.g., for PCIe cards) require careful layer routing to avoid trace congestion.

Reliability and Testing:

Blind/buried vias reduce via count and improve density but require rigorous impedance control. Automated optical inspection (AOI) and flying probe testing ensure no open/short circuits.

Compliance with JEDEC and IEEE standards is mandatory for signal integrity and thermal performance.

For example, a 24-layer server motherboard might include:

Layers 1–4: CPU/GPU signal routing (PCIe, memory).

Layers 5–8: Power planes (12V, 5V, 3.3V).

Layers 9–16: Backplane signals and storage interfaces.

Layers 17–24: Peripheral signals (USB, Ethernet) and ground planes.

Such designs prioritize scalability (support for multiple CPUs and expansion cards) and fault tolerance, with redundant power supplies and error-correcting code (ECC) memory interfaces. The use of advanced materials and precise layer stackups ensures server motherboards can handle the extreme demands of modern data centers, from AI workloads to high-frequency trading systems.